Data de postagem: 2015-06-15

It is true that almost all electronic devices require a clock, but only some applications require strict control over parameters such as phase jitter, spurious content, and frequency accuracy. For example, whether it is wireless, coaxial cable, twisted pair or fiber optic communication applications, there are strict requirements on clock parameters to achieve reliable links. As engineers strive to achieve higher data rates and increased port counts, the requirements for source clocks become more stringent. Engineers are inevitably looking for a solution that meets all requirements while providing the performance needed to maintain excellent link integrity. Using a more integrated clock generator can alleviate design challenges for engineers.

When considering today's trend toward higher port densities and data rates, engineers often face three major challenges. The first challenge is to generate a clock signal that meets the output center frequency and communication protocol frequency accuracy requirements. The second problem is that the signal must meet the phase noise or phase jitter requirements specified by the processor, SERDES, or ASIC manufacturer. The final test is that a higher number of ports needs to fan out the clock signal to multiple ICs, while minimizing the reduction in phase noise, which is due to multiple changes in fanout or signal level conversion. Caused by mixed phases.

To address the first challenge of generating a stable and low-noise output frequency, engineers often do not use quartz technology. Of course, there are other technologies, including MEMS (Micro Electro Mechanical Systems). However, quartz offers engineers the benefits of a high Q factor, temperature-dependent self-compensation, and reliability. A Q value greater than 100,000 results in low phase noise and easily meets -70dBc / Hz at a 10Hz offset. The use of special techniques can reduce phase noise. From -40 ° C to + 85 ° C, the self-compensating quality of the lattice keeps the resonant frequency within +/- 10 to +/- 20 parts per million (PPM), again meeting the requirements of most communication applications . If you need to guarantee stability below +/- 10PPM, you only need to perform external temperature compensation on the crystal. In addition,

The most commonly used quartz resonators have a fundamental frequency between 10MHz and 80MHz. Despite the abundance of suppliers at these frequencies, growing and processing quartz crystals still requires long lead times, and careful supply chain management is required. Shortages across the industry are frequent and largely unpredictable, as some high-volume applications (such as mobile phones) may take up crystal manufacturing capabilities. Supply chain management of quartz crystals can be a daunting task, especially for small organizations that may not have a direct relationship with large crystal suppliers.

Many communication links rely on a higher frequency reference, such as 156.25MHz for Ethernet and 212.5MHz for Fibre Channel. The challenge with crystals above 80MHz is that they must use unique manufacturing techniques and fewer crystal vendors support this frequency range.

Most communication applications rely on good frequency accuracy. For example, Ethernet and Fibre Channel do not specify a frequency drift of more than +/- 100PPM over the life of the device. Although quartz crystals can easily adapt to this situation, engineers must ensure that the mating interface between the crystal and the oscillator circuit is well controlled. Figure 1 shows an electrical model that can be used to calculate the center frequency of an oscillation. The parameters L1 (moving inductance), RR (series resistance), C1 (moving capacitance) and C0 (parallel capacitance) depend on the design and manufacture of the crystal, while CL (load capacitance) depends on the intentional and parasitic load generated by the external capacitor. Chip capacitors and stray capacitance of traces and amplifier gates.

Figure 1. The oscillation center frequency of a quartz oscillator depends on several parameters, including CL (including stray plates and device capacitance).

In most cases, crystal, capacitor and oscillator vendors have clearly specified all parameters. However, the effect of parasitic board capacitance is the responsibility of the system design engineer. Equation 1 below shows the possible effects of a small amount of excess trace capacitance. The parameter dFL is the total amount of frequency shift caused by the change in load capacitance (dCL). For the nominal values ??of C1, C0, and CL, a 1pF excess capacitor will change the output frequency by 76PPM. Considering the typical +/- 20PPM temperature drift and some aging, the frequency may be out of specification. Maintaining a controlled layout and considering all parasites is the key to good accuracy. Note that dFL is in units of PPM, C1 is in units of fF, and dCL, C0 and CL are in units of pF.

Formula 1: dFL = 2000 × C1 × dCL / (C0 + CL) 2

Figure 2 shows a cascaded PLL including a typical communication link. The clock generator provides the base clock for the transmitter. This clock is multiplied by the wire speed, the receiving PLL locks to the data at wire speed, and provides a clock for data recovery. The jitter transfer function of each PLL is a low-pass filter that tracks the low-frequency components of the clock phase noise, but suppresses phase noise above the cutoff frequency. This means that only a portion of the clock phase noise will affect the data output to the channel. The rest are filtered. In many cases, especially considering today's advanced SERDES designs, transmitters and receivers have very high cut-off frequencies, sometimes greater than 40 MHz. This means that most of the clock phase noise will pass through the transmitter clock multiplier and appear on the channel.

Figure 2. The bandwidth of the TX clock multiplier determines the portion of the clock phase jitter that appears on the communication channel.

Because only a portion of the jitter affects the communication link, ASIC and processor vendors specify an integrated frequency band. For OC-48, the integrated frequency band of interest is a 12kHz to 20MHz offset. However, most clock vendors have standardized standards that provide integrated phase noise from 12kHz to 20MHz, which is a common advantage that end users can compare one by one between competing devices. Today's processors require lower phase jitter over a wider integrated bandwidth, so a bandwidth of 12kHz to 40MHz must be specified on the clock.

The total clock phase jitter should account for a small portion of the overall jitter budget, typically 0.1 to 0.3 per unit interval. The unit interval at 12Gbps line rate is 83ps. In this case, the total clock jitter should be less than 8ps peak-to-peak. Considering a bit error rate of 10-12, the RMS phase jitter should not exceed 0.6ps. For 25Gbps line speed, the recommended RMS clock jitter is 0.3ps.

Producing such a low phase jitter clock is already challenging enough, but the requirement to fan out the clock signal to multiple devices complicates the challenge. Jitter requirements are not limited to clock generator sources, but refer to the total accumulated jitter in the entire clock tree. This is the last challenge in system design today. Fan-out requirements include requirements that all clocks require the same voltage and logic level type. For example, a 4-port 12G Fibre Channel switch might use multiple copies of the 212.5MHz low-jitter clock reference, all LVDS logic, and all be powered by a 2.5V power supply. Other devices (such as FPGAs) may require four outputs using LVDS output logic, while two use LVCMOS. In many cases, the fan-out phase may constitute a continuity (and more often an interrupt) condition to meet jitter requirements.

When cascading multiple stages, Equation 2 explains the total RMS phase jitter. The total jitter is the rms sum of the individual RMS jitter values. When cascading fan-out stages, the end user must ensure that the cumulative amount of RMS phase jitter is not sufficient to degrade link quality. Using a clock generator with 0.25ps RMS phase jitter and cascading a fan-out buffer with 0.5ps additional RMS jitter will reduce the overall performance to 0.56ps RMS. Cascading multiple stages can also introduce jitter due to poor signal integrity or power supply noise.

By using a highly integrated clock generator, you can find a faster, easier, and more efficient way to implement a clock tree. This clock generator with integrated output buffers reduces the burden of calculating phase jitter in cascaded components. Such devices accept low-cost crystals. Generate the required output frequency, multiply if necessary, and fan out to multiple clocks. The ability to mix and match output logic types and output supply voltage rails on the same device provides an additional convenience that saves component count and speeds design time. As long as the crystal recommendations are strictly adhered to, the end user can achieve 200fs output jitter at the output of the fan-out stage, including the effects of crosstalk, while maintaining strict frequency accuracy.

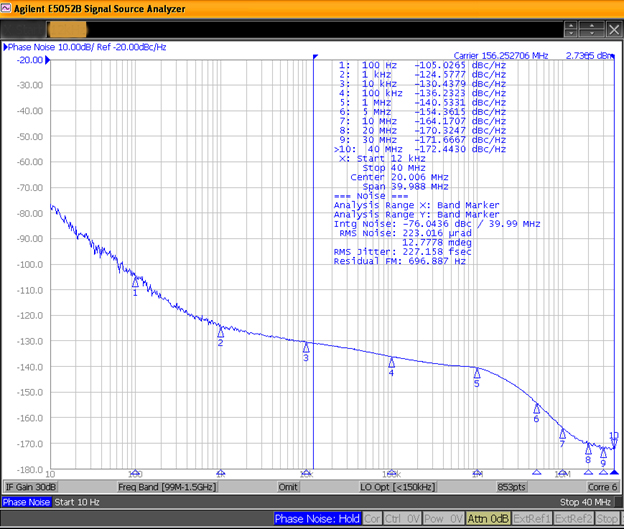

To achieve the highest level of integration and simplify the design, fully integrated clock generators (such as the MX85) not only have all the advantages of a highly integrated clock, but also an integrated crystal. By integrating crystals, these devices eliminate design and supply chain issues related to quartz. The end user will get a device with a small 5mm x 7mm form factor that is guaranteed to produce output frequency tolerances that can produce up to two frequencies. The tightly coupled on-chip fan-out stage has ultra-low noise and can provide industry-leading 227fs RMS phase jitter even in a wide integrated frequency band from 12kHz to 40MHz, as shown in Figure 3. This meets the requirements for next-generation communication standards, while reducing board space and all the design challenges traditionally imposed by clocks and timing.

Figure 3. The MX852BB0030 integrates the entire clock tree including crystals and fan-out buffers, resulting in an amazing 227fs RMS phase jitter over the extended integrated frequency band from 12kHz to 40MHz.

In summary, there are several alternatives that can meet the combination of frequency accuracy, ultra-low phase jitter, and high fan-out required by next-generation end systems. Today's highly integrated clock solutions provide performance while avoiding the design risks, complexity, and analysis of crystal design, quartz crystal supply chain management, and cascading multiple PLL clock generators and large fan-out buffers.