The ATF20V8B is a high performance CMOS(electrically erasable) programmable logic device (PLD) using Atmel's proven electrically erasable flash memory technology. The speed can reach 7.5 ns and the power consumption is as low as 10 mA. All speed ranges are specified in excess of the 5V±10% industrial temperature range and 5V±5% commercial temperature range. Several low power options allow the selection of the best solution for various types of power limited applications.

Pin Configurations

All of these options significantly reduce the total system power and improve system reliability. The ATF20V8B integrates a superset of common architectures, allowing a direct replacement for the 20R8 family and most 24-pin composite PLDS. Each of the eight outputs is assigned eight product terms. Three different modes of operation, automatically configured by the software, allow highly complex logic functions to be implemented.

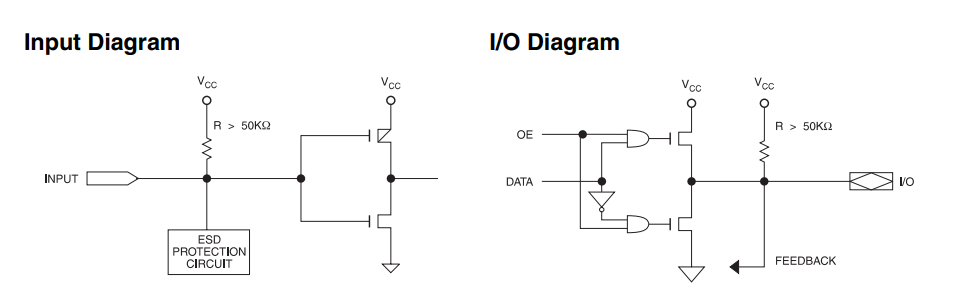

Functional Logic Diagram Description

The logical options diagram and function diagram describe the ATF20V8B architecture. Eight configurable macro units can be configured for registered output, combined I/O, combined output, or dedicated input. The ATF20V8B can be configured in three different modes. Each mode makes the ATF20V8B look like a different device. Most PLD compilers can automatically select the correct mode.

The user can also force selection by providing a schema selection to the compiler. The determining factor is whether to use registers or composite output, dedicated output or output with output enable control. ATF20V8B Universal architecture programmable emulation of many 24-pin PAL devices.

These architectural subsets can be found in each of the configuration patterns described in the following pages. The user can download the listed subset of device JEDEC programming files to the PLD programmer, and the ATF20V8B can be configured to resemble the selected device. Check with your programmer manufacturer for this feature. The compiler automatically disables unused product terms to reduce power consumption. Safety fuse, when programmed, protects the contents of ATF20V8B.

Eight bytes (64 fuses) of the user's signature are accessible to the user to store the item name, part number, revision, or date, and so on. The user signature is accessible regardless of the state of the security fuse.

Block Diagram